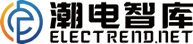

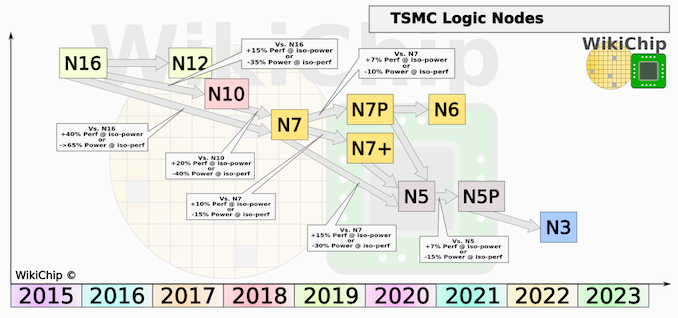

在今天的IEEE國際電子器件大會(IEDM 2019)上,臺積電概述了其在5nm工藝上取得的初步成果。目前,該公司正在向客戶提供基于N7和N7P工藝的產品。但在向5nm進發(fā)的時候,兩者賈昂共享一些設計規(guī)則。據悉,與7nm衍生工藝相比,N5新工藝將增加完整的節(jié)點,并在10層以上廣泛使用EUV技術,以減少7nm+制程的總步驟。此外,臺積電會用上第五代FinFET技術。

?。}圖via AnandTech)

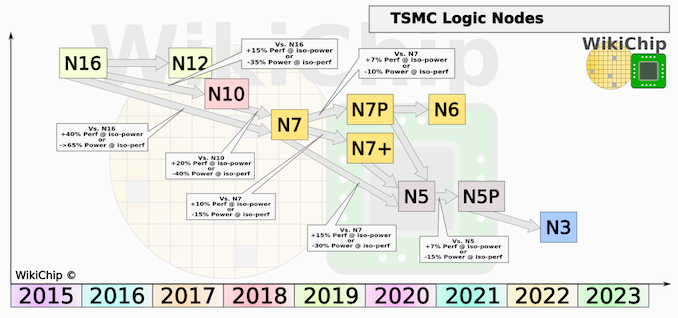

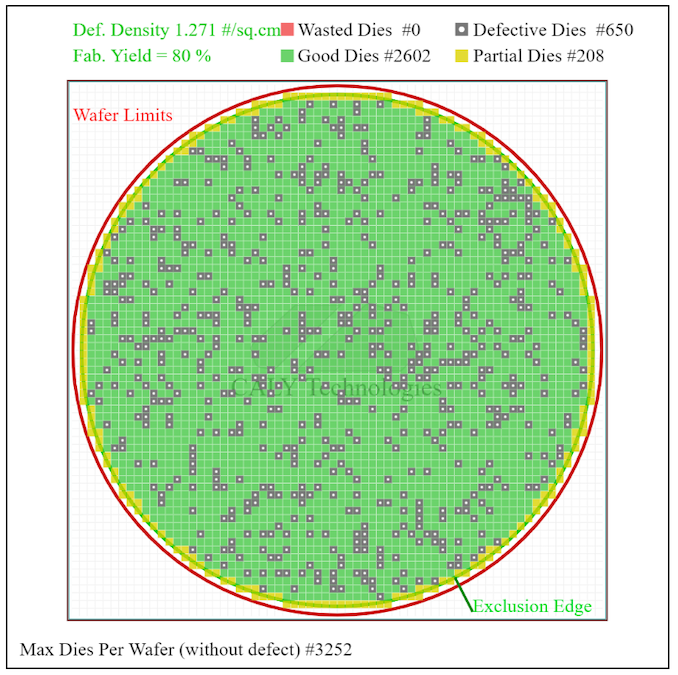

TSMC表示,其5nm EUV可將密度提升約1.84倍、能效提升15%(功耗降低30%)。當前測試的芯片有256 Mb SRAM和一些邏輯器件,平均良率為80%、峰值為90%。

顯然,盡管新工藝能夠縮小現代移動芯片的大小,但收益率要低得多。目前新技術正在處于早期測試階段,預計可在2020上半年轉入量產,預計5nm成品芯片可在2020下半年準備就緒。

目前TSMC 7 nm工藝可在每平方面積上堆積1億個晶體管(約96.27 mTr/mm2),5nm新工藝可達177.14 mTr/mm2

作為試產的一部分,TSMC會制造大量的測試芯片,以驗證新工藝是否如預期般推進。其中包括一種靜態(tài)隨機存儲(SRAM),以及一種SRAM+邏輯I/O芯片。

TSMC展示了具有大電流(HC)和高密度(HD)特性的SRAM單元,尺寸分別為25000/21000平方納米。同時,該公司正在積極推廣有史以來最小的HD SRAM。

至于組合芯片,TSMC表示其包含了30%SRAM、60%邏輯(CPU/GPU)、以及10%的IO組件。SRAM部分為256 Mb,所占面積為5.376平方毫米。

不過TSMC指出,該芯片不包含自修復電路,意味著我們無需添加額外的晶體管,即可實現這一功能。若SRAM占芯片的30%,則整個芯片面積為17.92平方毫米左右。

目前TSMC公布的平均良率約為80%,單片晶圓的峰值良率則高于90%。但17.92平方毫米的面積,意味著它并非高性能的現代工藝芯片。

通常情況下,芯片制造商會首先咋移動處理器上小試牛刀,以分攤新工藝的高昂成本嗎,比如基于7nm EUV的麒麟990 5G SoC(面積接近110平方毫米)。

盡管AMD Zen 2芯片看起來很大,但并非所有組件都采用EUV工藝生產。不過展望未來,它也更適合遷移至5nm EUV。

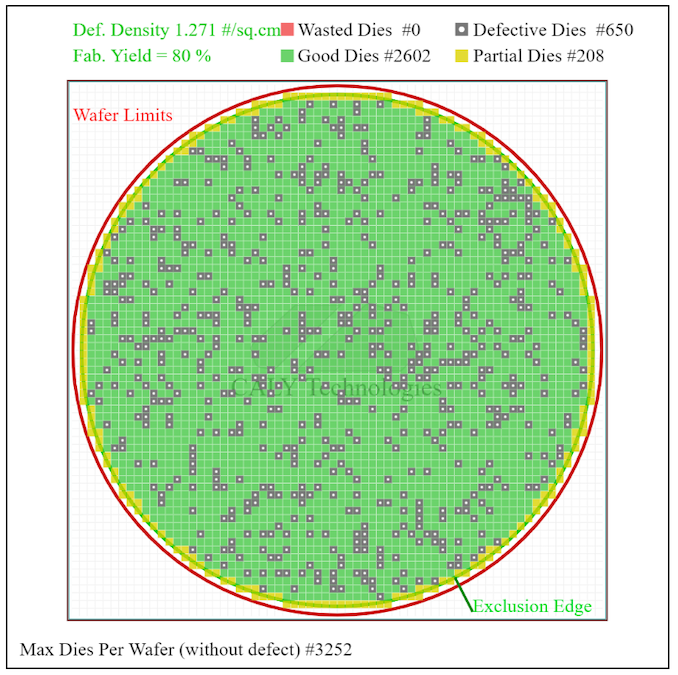

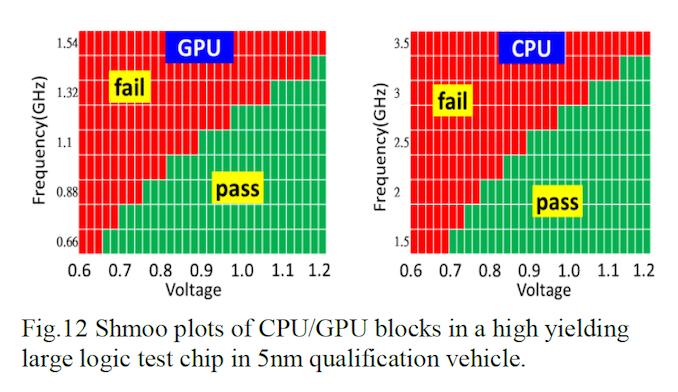

在臺積電試產的CPU和GPU芯片中,眼尖的網友,應該可以看出一些端倪,比如通過芯片可以達成的頻率來逆推良率。

在TSMC公布的數據中,CPU可在0.7 V電壓下實現1.5GHz主頻,并在1.2 V電壓下達成3.25 GHz頻率。

至于GPU,圖中顯示可在0.65 V時實現0.66 GHz頻率,并在1.2V電壓下提升至1.43 GHz。

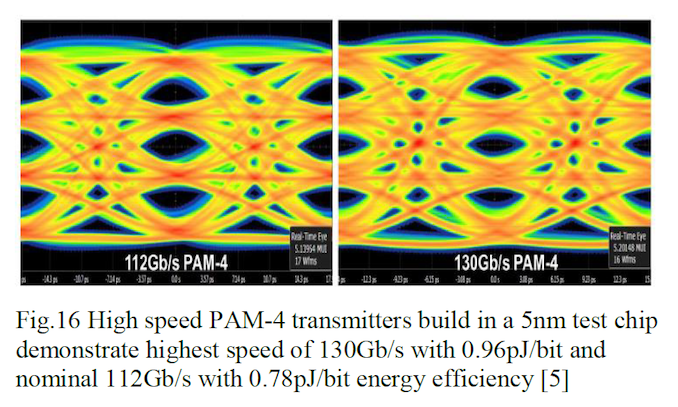

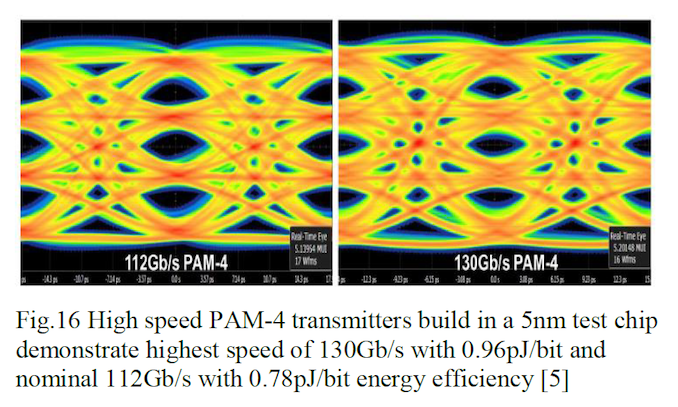

對于未來的芯片來說,支持多種通信技術,也是一項重要的能力。因此在測試芯片中,TSMC還介紹了高速PAM-4收發(fā)器。

此前,我們已在其它地方見到過112 Gb/s的收發(fā)器。而TSMC能夠以0.76 pJ/bit的能源效率,達成同樣是速率。

若進一步推動帶寬,TSMC還可在肉眼可見的公差范圍內取得130 Gb/s的成績,且此時能效為0.96 pJ/bit。(對PCIe 6.0等新技術來說是好事)

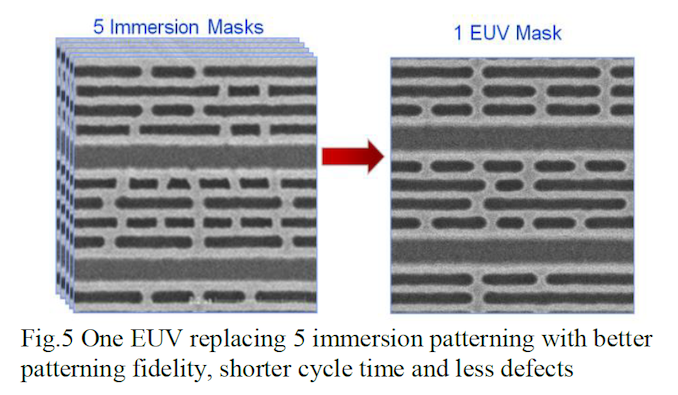

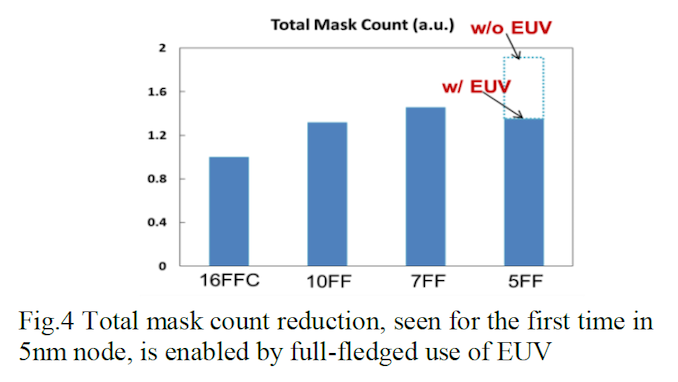

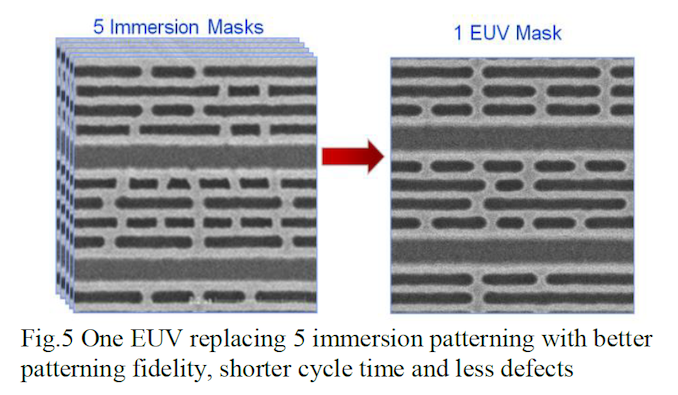

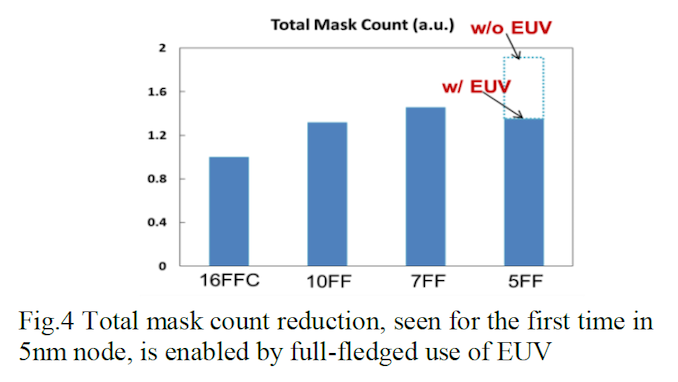

為了改進越來越復雜的EUV工藝,TSMC在基于193 nm的ArF浸沒式光刻技術上花費了很多心思。曾經28nm制程的30~40道掩膜,現已在14/10nm上增加到了70道。

有報道稱,一些領先的工藝,甚至超過了100道掩膜。好消息是,TSMC在文中表示,其將在10曾以上的設計中廣泛使用精簡掩膜的新技術。

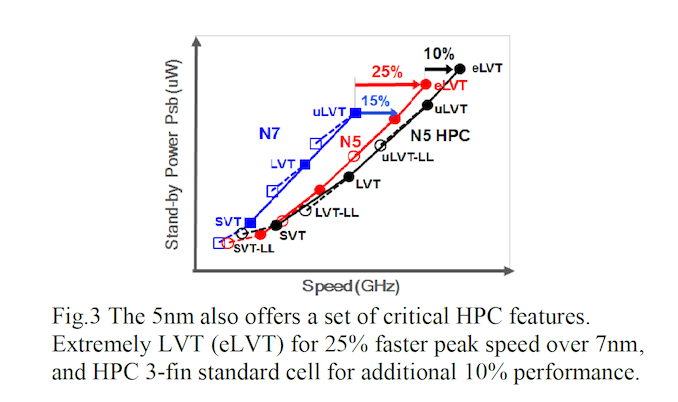

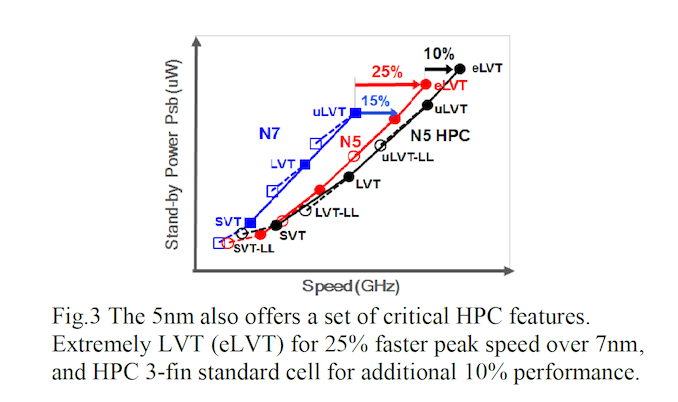

在IEDM上,TSMC還描述了七種不同的晶體管供客戶挑選,包括高端的eVT和低端的SVT-LL,uLVT、LVT和SVT(這三種都是低泄漏/LL的衍生版本),以及從uLVT大幅跳躍到的eLVT。